Designing a reliable and robust high-voltage inverter starts with a foundational principle in PCB layout—minimizing current loops. This is not just a best practice; it is essential to performance, safety, and electromagnetic compatibility (EMC).

Just as we identify flux loops in motor design, we must identify and control current loops during the layout of an inverter. This becomes increasingly critical as bus voltages climb—700V and beyond is not uncommon in modern motor drives and electric vehicle inverters.

Why Short Current Loops Are Critical

Long or poorly routed current loops create parasitic inductance, which can lead to:

- Voltage spikes

- High-frequency ringing

- Increased EMI

- Signal integrity issues, especially in sensitive gate-drive and control circuits.

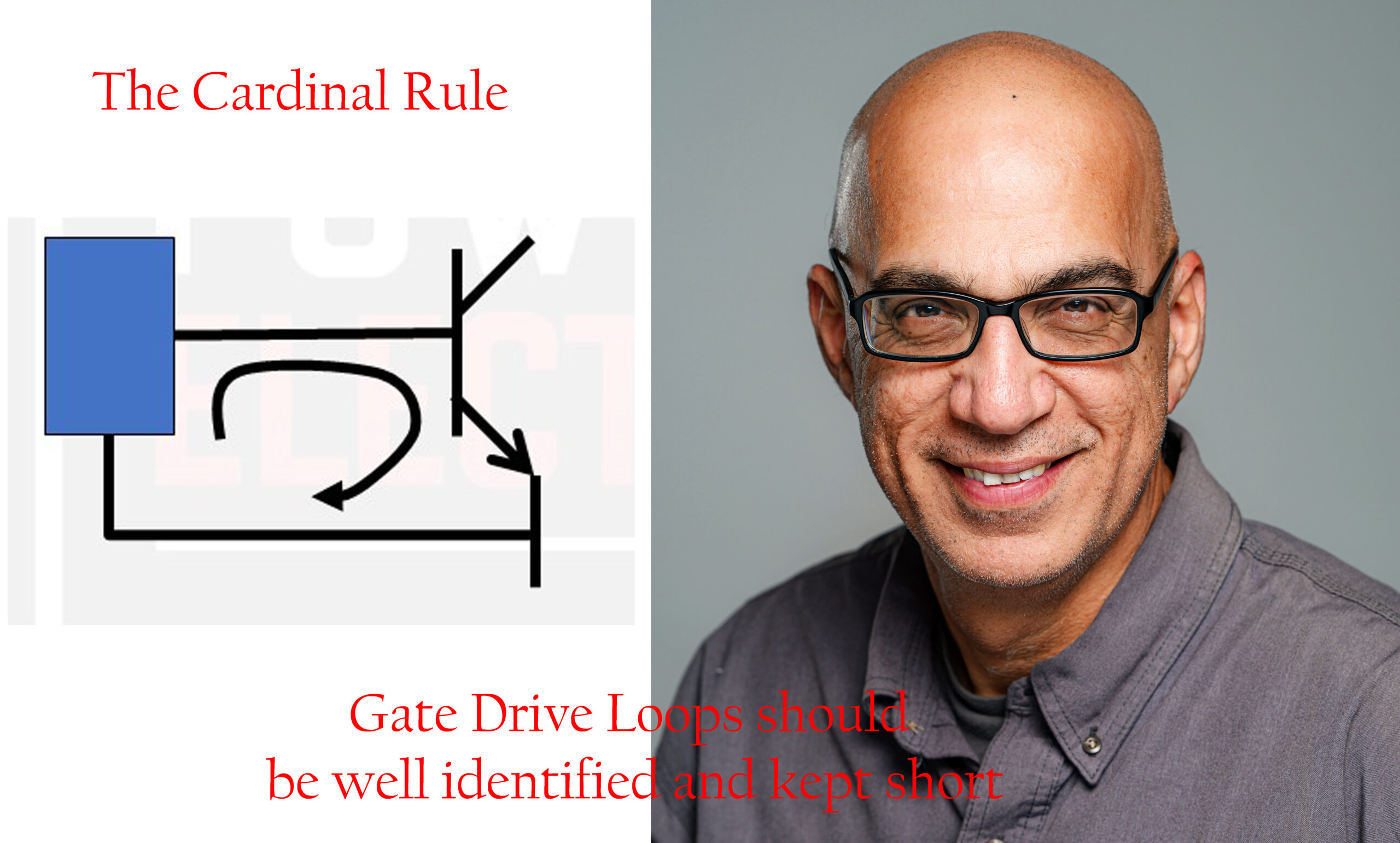

One core layout strategy to combat this is to keep all current-carrying traces short and tightly looped, especially in the gate drive paths of IGBTs or MOSFETs. Gate drive loops are particularly sensitive due to their switching nature and proximity to high-voltage transitions.

Gate Drive Layout Best Practices

When designing for high voltage (e.g., 700V bus), special care must be taken in gate drive layout:

- Keep gate drive traces short and direct

- Minimize the dV/dt coupling to nearby control traces and microcontroller/DSP lines

- Place gate driver ICs as close as possible to the power switches

Fast switching edges (high dV/dt) can inject noise into control circuits, leading to erratic behavior or failures in microcontrollers or DSPs if not adequately mitigated.

The Role of Planes and Capacitors

To control impedance and support clean power switching:

- Use a VBUS plane on the PCB to distribute high voltage uniformly

- Place film and electrolytic capacitors close to the switching devices (e.g., IGBTs/MOSFETs)

- Ensure low impedance paths from the VBUS plane to the drain of the high-side switch, and from the source of the low-side switch to the power ground.

A correctly implemented power plane reduces the loop area and inductance, stabilizing the inverter operation under rapid switching conditions.

Bus Bar Design for High-Power Drives

In high-current applications, PCBs alone may not suffice. That’s where bus bars come into play:

- Use stacked or laminated bus bars to connect VBUS and ground to IGBTs

- Place the grounding bus bar directly on top of the switching devices to reduce loop area

- Aim for a sandwich-style configuration: VBUS bus bar, power devices, then ground bar

This structure minimizes impedance and enhances thermal performance and mechanical reliability.

Internal Planes and Impedance Control

In multilayer PCBs, internal planes provide another avenue for managing loop inductance and EMI:

- Use internal VBUS and ground planes to minimize parasitics further

- Consider buried capacitance techniques between the power and ground layers

- Route sensitive signals away from noisy power switching zones

The overall goal is impedance control, signal integrity for communication traces, and power integrity for switching devices.

Final Thoughts

The physical layout of a power electronics system is as critical as the electrical schematic. Even the best-designed circuit will fail to deliver if the current loops are long, noisy, or poorly controlled. Keeping your current loops short, tight, and impedance-optimized improves reliability, reduces EMI, and builds a foundation for scalable, high-performance inverter systems.

Whether building low-voltage motor drives or megawatt-scale converters, layout discipline differentiates between success and struggle.

Leave a Reply